Side

« forrige 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 næste »

Gå til:

AMD Phenom 9600

Af Allan Nielsen | 24-03-2008 | 36047 visninger | 14 kommentarer

K10 Arkitektur

Native quad core

Phenom er bygget på AMD's K10 arkitektur, der er en opdatering af den efterhånden aldrende K8.

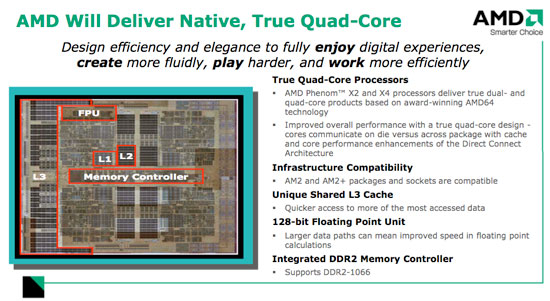

K10 er baseret på 65nm teknologi, og AMD gør et stort nummer ud af at påpege, at der er tale om en såkaldt "native quad core" processor, og hvad betyder det så? Hvis vi kigger lidt tilbage i tiden, så er historien den samme som da de med lanceringen af X2 havde en "native dual core" CPU. Dette betød at chippen oprindeligt var designet til at bære de 2 kerner, imens Intels løsning mere eller mindre var at proppe to ens kerner i én indpakning, uden at have en dedikeret kommunikationslinie imellem kernerne. AMDs løsning er uden tvivl den mest elegante, ud fra et arkitekturmæssigt synspunkt - og det samme gør sig nu gældende med Phenom. Her har AMD opbygget en 4-kernet chip fra bunden, imens Intel endnu engang har haft held med at proppe 2 ens kerner (nu 2 dual cores) ned i én pakning. Faktum er dog, at en god arkitektur på dette punkt ikke nødvendigvis kommer til udtryk som ekstra performance i den virkelige verden, og ordet "native" er derfor mere en salgsgimmick end et udtryk for en hurtigere processor.

Opbygning

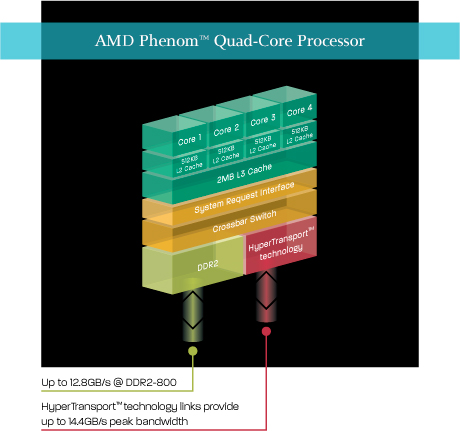

Lad os gennemgå arkitekturen fra toppen og nedad. Øverst på figuren ses de 4 kerner (cores), nummerede 1 til 4. Hvad der ikke er vist på figuren, er kernernes interne level 1 cache, der ialt udgør 128 kb, fordelt på data og instruktionscache, med 64 kb til hver. Under kernerne ses deres dedikerede level 2 cache lager, som fungerer helt som vi er vant til, dvs. hver kerne har sit eget L2 cache. Samlet set er der 2 MB level 2 cache (4x512 kb).

Det er først i det næste lag, at vi ser en af de store nyheder i Phenom, nemlig en level 3 cache. Dette cache lager er delt imellem kernerne, og er totalt 2 MB, dvs. en fordobling af den samlede cache mængde. Det spændende ved L3 cachen er, at den er delt. Det betyder groft sagt, at hvis en applikation kun gør brug af én af kernerne, og de andre 3 kerner mere eller mindre er "arbejdsløse", så vil den arbejdende kerne have samtlige 2 MB L3 cache til rådighed. Dette er naturligvis især interessant for cache-sultne programmer. L3 er som nævnt et delt cache lager, kaldet et victim cache. Heri smides "ubrugte" data fra L2, dvs. victim data. Der er ingen direkte forbindelse imellem kernerne på L1 og L2 niveau, det er kun L3 der er delt (noget AMD kalder BSC - "Balanced Smart Cache".) Det kan nævnes at der benyttes en round-robin lignende algoritme ved tilgangen til L3, dvs. fordeling af L3 imellem kernerne.

Under cachen, kommer SRI'en - System Request Interface, der er velkendt blandt quad-core AMD folket. Det er kort fortalt en mekanisme der gør de 4 kerner i stand til at kommunikere med hinanden. Næste lag er en Crossbar switch, der styrer adgangen til de eksterne ressourcer (hukommelse og HTT) for alle 4 kerner

Mange vil nok undre sig over at der på figuren ovenfor står DDR2-800, når vi tidligere har beskrevet at der understøttes op til DDR2-1066. Dette har sin enkle forklaring i, at der officielt først understøttes DDR2-1066 når dennes specifikation er helt på plads. Dette var ikke tilfældet på frigivelsestidspunktet af Phenom, så AMD skriver flere steder DDR2-800, og andre steder "DDR2-1066 (Pending JDEC approval and release og DDR2-1066 specification)".

Nye tiltag

AMD har dog lavet andet end blot at tilføje kerner, og en ekstra pulje cache. Der er blevet plads til forbedringer af SSE og kommatalsberegninger, de såkaldte floating points. Virtualiseringen skulle efter sigende også være forbedret, hvilket naturligvis er spændende, når man forestiller sig arkitekturen brugt i f.eks. servermiljøer. Virtualisering er stadig ikke noget de fleste af os som privatpersoner har nogen gavn af, og for langt størstedelen af de solgte Phenoms til personlig brug, vil virtualisering aldrig blive benyttet. Vi vil derfor ikke grave dybere i emnet her.

Med Phenom kommer til gengæld noget andet, som er mere jordnært for de fleste, nemlig en mere avanceret strømstyring, der muliggør individuel styring af hver kerne - en teknologi AMD kalder CoolCore.

Med denne teknologi sparer CPU'en strøm, da den lukker ned for de dele, der ikke lige er i brug. F.eks. kan memory controlleren lukke ned for skrive-logikken når den er igang med at læse fra hukommelsen, hvilket betyder et mere optimeret strømforbrug, hvilket også ses i den opnåede rating på 95 W i max effekt. Hvis vi skruer tiden en anelse tilbage vil de fleste huske at X2'erne kom frem med en 110 W rating, imens de daværende FX modeller kom op på 105 W, så nutidens 4 kerner på samlet 95 W er et skridt i den rigtige retning.

TLB problemet

De fleste har nok hørt om TLB problemet på de første udgaver af Phenom - også mere officielt omtalt som "Erratum 298". TLB er en forkortelse for Translation Lookaside Buffer, og en sådan buffer bruges til at finde specifikke data i et virtuelt adresseområde. I sjældne situationer har der opstået fejl, der har betydet at forkerte TLB data blev skrevet i L3 cachen, inden de blev opdateret i L2. Problemet opstår i forbindelse med brug af virtualisering, samtidig med ekstrem processorbelastning. Den generelle holdning på Internettet synes at være, at problemet er så godt som ikke-eksisterende, og det er svært at finde nogen der påviseligt har oplevet fejlen. På HardwareOnline.dk redaktionen har vi ikke oplevet fejlen, og processoren har generelt virket utrolig stabil og pålidelig.

Hvorom alting er, så har der været arbejdet på højtryk for at sikre, at problemet ikke kan ske. Der er derfor udgivet patches til at sikre dette - med det resultat, at mange har oplevet problemer med fald i performance, mange steder rapporteres om op til 10%. Vores holdning er primært, at der naturligvis ikke skal være store fejl i processorer, men at der her har været tale om en storm i et glas vand. Det er langt de færreste der vil opleve problemet, hvis de vælger at undlade opdateringen.